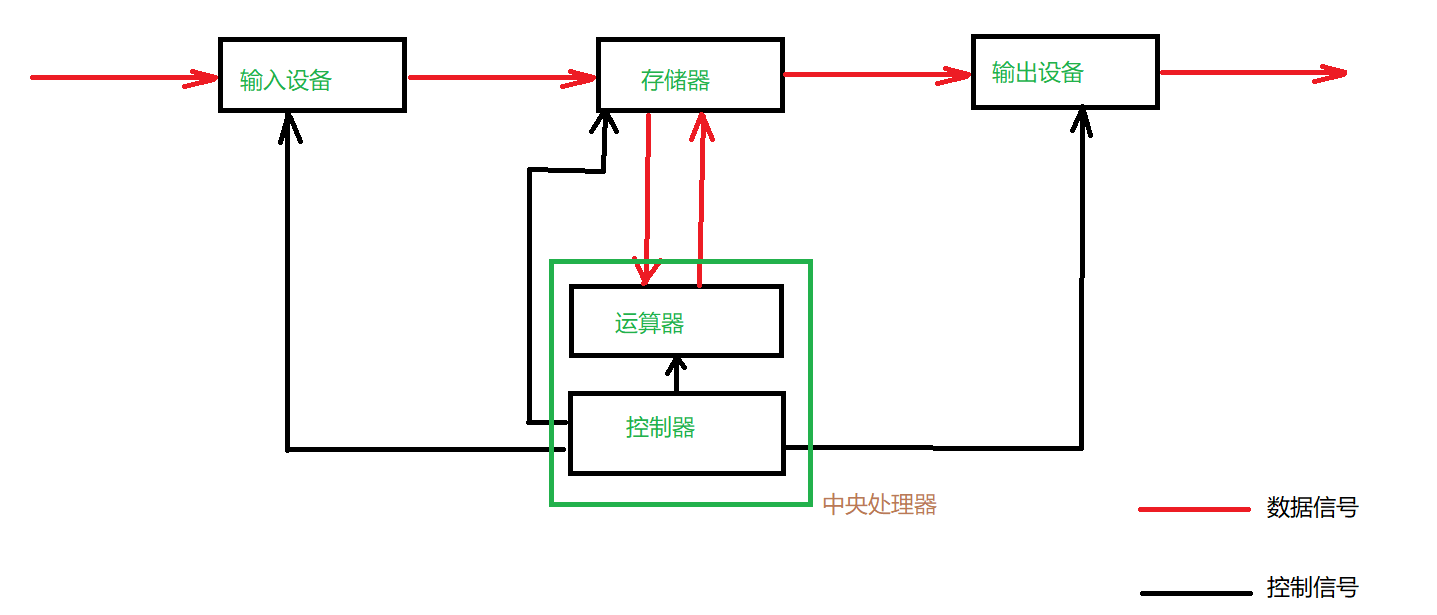

冯诺依曼架构

冯诺依曼计算机特点

- 计算机由运算器、控制器、存储器、输入设备、输出设备五大部件组成

- 指令与数据以同等地位存放在存储器,并可按地址寻访

- 指令与数据均以二进制数表示

- 指令由操作码和地址码组成,操作码用来表示操作的性质,地址码用来表示操作数在存储器中的位置

- 指令在存储器中顺序存放。通常也顺序执行,在特定条件下,可根据运算结果或设定条件改变执行顺序

- 机器以运算器为中心,输入输出设备与存储器间的数据传递通过运算器完成

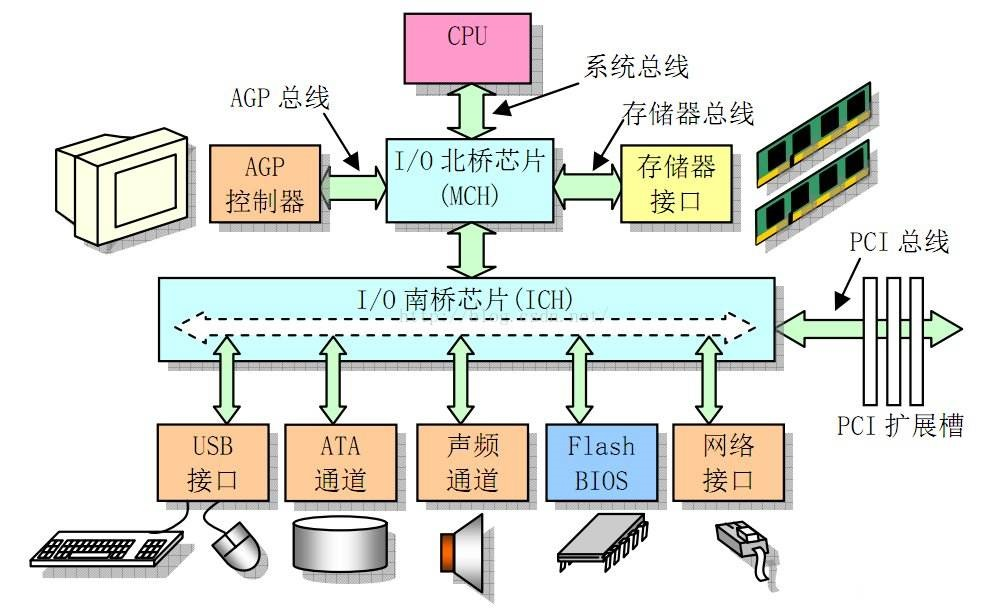

细化的计算机组成框架

主存储器

- 主存储器包括存储体M、各种逻辑部件及控制电路。存储体由许多存储单元组成,每个存储单元包含若干个存储元件(称存储元、存储基元),每个存储元件能寄存以为二进制代码

- 主存的工作方式是按存储单元的地址号来实现对存储字各位的存(写)、取(读)。这种存取方式称为按地址存取方式,即按地址访问存储器(简称访存)

- 为了能实现按址访问的方式,主存中还需要配置两个寄存器MAR和MDR

MAR

(Memory Address Register)是存储器地址寄存器,用来存放欲访问的存储单元的地址,其位数对应存储单元的个数(如MAR为10 位,则由210=1024个存储单元,记为1K)MDR(Memory Data Register)是存储器数据寄存器,用来存放从存储体的某个单元取出的代码或者准备往某个存储单元存入的代码,其位数与存储字长相等

- 现代计算机为了适应指令和是字长可变,其长度不由存储字长来确定,而是由字节的个数来表示,1个字节(byte)被定义为8位(bit)二进制代码组成,此时存储字长、指令字长、数据字长三者可不相等,但必须是字节整数倍

运算器

- 运算器最少包括3个寄存器(现代计算机内部往往设有通用寄存器组)和一个算术逻辑部件(ALU)。其中ACC为累加器、MQ为商乘寄存器、X为操作数寄存器,这三个寄存器完成不同运算时,所放的操作数也各不相同

- ACC在加法运算中存储被加数以及和;在减法运算中存储被减数以及差;乘法运算中存储乘积高位;在除法运算中存储被除数以及余数,MQ在乘法运算中存储乘数以及乘积低位;在除法运算中存储商,X在加法运算中存储加数;在减法运算中存储减数;在乘法运算中存储被乘数;在除法运算中存储除数

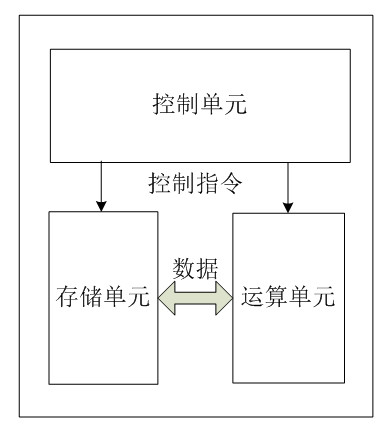

控制器

- 控制器是计算机的神经中枢,由他指挥各部件自动、协调地工作。具体而言它首先要命令存储器读出一条指令,称为取址过程。接着对该指令分析,指出该指令要完成的操作,并按寻址特征指明操作数的地址,称为分析过程。最后根据操作数所在的地址及指令的操作码完成操作,称为执行过程。

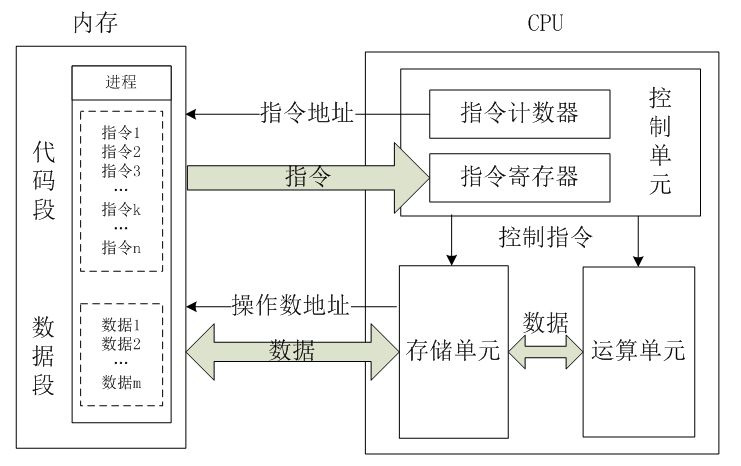

- 控制器由程序计数器(Program Counter,PC)、指令寄存器(Instruction Register)以及控制单元(Control Unit,CU)

- PC用来存放当前欲执行指令的地址,它与主存的MAR之间有一条直接通路,并具有自动加1功能,即可自动形成下一条指令的地址。

- IR用来存放当前的指令,IR的内容来自主存的MDR,IR中的操作码(OP(IR))送至CU,记作OP(IR)**→**CU,用来分析指令;其地址码(Ad(IR))作为操作数的地址送至存储器的MAR,记作

Ad(IR)→MAR - CU用来分析当前指令所需要完成的操作,并发出各种微操作命令序列,用以控制所以被控的对象

CPU工作过程

控制单元在时序脉冲的作用下,将指令计数器里所指向的指令地址(这个地址是在内存里的)送到地址总线上去,然后CPU将这个地址里的指令读到指令寄存器进行译码。对于执行指令过程中所需要用到的数据,会将数据地址也送到地址总线,然后CPU把数据读到CPU的内部存储单元(就是内部寄存器)暂存起来,最后命令运算单元对数据进行处理加工。周而复始,一直这样执行下去!